# TP44220HB – 650 V GaN Half-Bridge, 180 m $\Omega$ (LS) and 180 m $\Omega$ (HS)

### 1.0 Features

- 650 V enhancement mode power HEMTs

- $R_{DSON}$ : 180 m $\Omega$  (Low-side) and 180 m $\Omega$  (High-side)

- IDS: 10 A (max) / IDSpulse: 15 A (max)

- Adjustable turn-on/off speed

- Reverse conduction capability

- Zero reverse-recovery loss

- High switching frequency capability

- Interfaces with 6 V and ≥12 V drivers (see Application **Information**)

- Low-side thermal-pad LV-isolated from the source for better thermal connection even with current-sense resistors

(Top View)

Figure 1 Device Image (30 pin 8×10×0.8 mm QFN Package)

## 2.0 Topologies and Applications

- Ac-dc, dc-dc, dc-ac converters

- Totem-pole and bi-directional PFCs

- Half- and full-bridge LLC converters

- High-frequency electronic transformers

- Mobile chargers and laptop adapters

- LED and motor drives

- Server power supplies

- Inverters

## RoHS/REACH/Halogen Free Compliance

## 3.0 Description

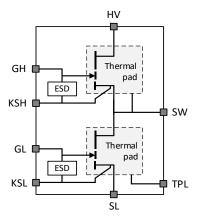

The TP44220HB is a half-bridge IC consisting of two 650 V GaN HEMT power devices. The low-side (LS) and the high-side (HS) devices are of 180  $m\Omega$  each. This co-packaged solution minimizes inductance in the power loop enabling clean switching even at high-current high-frequency operations. As provided in the application information, simple external interface circuits can be used to drive this part both from dedicated 6 V GaN drivers as well as more traditional 12 V drivers. Resistors in the individual gate path can be used to control the switching speeds of the lowside/high-side for the best EMI performance. The solution is well suited for all half-bridge applications with a view towards high performance and compact solution.

Figure 2 Functional Block Diagram

# 4.0 Ordering Information

**Table 1 Ordering Information**

| Base Part<br>Number | Package Type              | Form          | Qty  | Reel<br>Diameter | Reel<br>Width | Orderable<br>Part Number |

|---------------------|---------------------------|---------------|------|------------------|---------------|--------------------------|

| TP44220HB           | 30 Pin<br>8×10×0.8 mm QFN | Tape and Reel | 1000 | 13" (330 mm)     | 18 mm         | TP44220HBTRPBF           |

## 5.0 Pin Definition

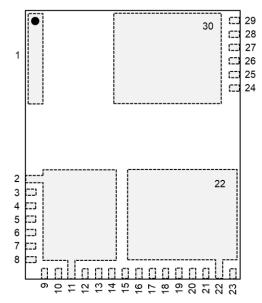

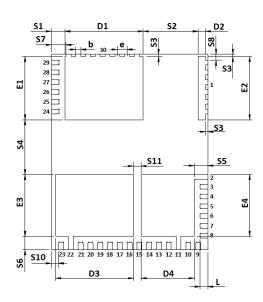

Figure 3 Pin Location (Package Top View)

**Table 2 Pin Definition**

| Pin Number          | Pin Name | Pin Type | Description                                                                                                                                                                                                                                                  |

|---------------------|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                   | HV       | PWR      | Drain of the high-side HEMT.                                                                                                                                                                                                                                 |

| 2, 11               | PADL     | NC       | No server d                                                                                                                                                                                                                                                  |

| 3–10, 12, 13,<br>23 | NCL      | NC       | No connect. These may be connected to TPL (Pin-22) for better PCB layout.                                                                                                                                                                                    |

| 14                  | GL       | Al       | Gate of the low-side.                                                                                                                                                                                                                                        |

| 15                  | KSL      | Al       | Kelvin-source of the low-side.                                                                                                                                                                                                                               |

| 16–21               | SL       | PWR      | Source of the low-side.                                                                                                                                                                                                                                      |

| 22                  | TPL      | Thermal  | Exposed thermal pad of the low-side. Must have good thermal path to the PCB thermal plane. Also, voltage difference between this pin and SL (Pin-16 to 21) shall be limited within ±20 V. See the section on Application Information for more details.       |

| 24                  | GH       | Al       | Gate of the high-side.                                                                                                                                                                                                                                       |

| 25                  | KSH      | Al       | Kelvin-source of the high-side.                                                                                                                                                                                                                              |

| 26–29               | NCH      | NC       | No connect. These may be connected to SW (Pin-30) for better PCB layout.                                                                                                                                                                                     |

| 30                  | sw       | PWR      | Half-bridge switching-node. Also exposed thermal pad of the high-side. Must connect to sufficient area of thermal plane either directly or through multiple thermal vias for effective cooling. See the section on Application Information for more details. |

**Abbreviations:** NC = not connected; AI = analog input; PWR = power

## 6.0 Absolute Maximum Ratings

Table 3 Absolute Maximum Ratings [1] @T<sub>J</sub> = +25 °C, unless otherwise specified.

The low-side and the high-side power devices are the same, and each of the parameter value, including electrical and thermal is for one of the individual devices, except if mentioned otherwise.

| Parameter                                                                 | Symbol                     | Value       | Unit |  |  |  |  |  |

|---------------------------------------------------------------------------|----------------------------|-------------|------|--|--|--|--|--|

| Electrical Ratings                                                        |                            |             |      |  |  |  |  |  |

| Drain to source voltage of GaN power HEMT                                 | V <sub>DS</sub>            | 650         | V    |  |  |  |  |  |

| Transient drain to source voltage [2]                                     | V <sub>TDS</sub>           | 750         | V    |  |  |  |  |  |

| Continuous drain current (at Tc = 25 °C)                                  | I <sub>DS</sub>            | 10          | А    |  |  |  |  |  |

| Continuous drain current (at Tc = 100 °C)                                 | I <sub>DS</sub>            | 6.5         | А    |  |  |  |  |  |

| Pulsed drain current (at T <sub>J</sub> = 25 °C) [3]                      | I <sub>DSpulse</sub>       | 15          | А    |  |  |  |  |  |

| Drain to source voltage slew-rate                                         | (dv/dt) <sub>DS</sub>      | 200         | V/ns |  |  |  |  |  |

| Input gate voltage with respect to the respective Kelvin-source           | V <sub>G</sub> s           | 6.5         | V    |  |  |  |  |  |

| Transient input gate voltage with respect to the respective Kelvin-source | V <sub>GS(Transient)</sub> | +9.0        | V    |  |  |  |  |  |

| Voltage difference of TPL pad to SL Pin                                   | ΔVTPL-Source               | ±20         | V    |  |  |  |  |  |

| Storage temperature range                                                 | T <sub>st</sub>            | −55 to +150 | °C   |  |  |  |  |  |

| Operating temperature range                                               | T <sub>op</sub>            | −55 to +150 | °C   |  |  |  |  |  |

| Maximum junction temperature                                              | TJ                         | +150        | °C   |  |  |  |  |  |

| Thermal Rat                                                               | ings                       |             | •    |  |  |  |  |  |

| Thermal resistance (junction-to-case) – bottom side [4]                   | R <sub>θ</sub> JC          | 2.0         | °C/W |  |  |  |  |  |

| Thermal resistance (junction-to-ambient) [4]                              | R <sub>θ</sub> ЈА          | 45          | °C/W |  |  |  |  |  |

| Soldering temperature                                                     | T <sub>SOLD</sub>          | 260         | °C   |  |  |  |  |  |

| ESD Ratings                                                               |                            |             |      |  |  |  |  |  |

| Human body model (HBM) per JS-001-2017                                    | Level 2                    | >2500       | V    |  |  |  |  |  |

| Charged device model (CDM) per JS-002-2014                                | Level C3                   | ≥1000       | V    |  |  |  |  |  |

| Moisture Ra                                                               | ting                       |             |      |  |  |  |  |  |

| Moisture sensitivity level (per J-STD-020D.1)                             | MSL                        | 1           | -    |  |  |  |  |  |

### Note:

- [1] These are stress ratings. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Exceeding one or a combination of the absolute maximum ratings may cause permanent and irreversible damage to the device and/or to the surrounding circuit.

- [2] For duration < 1ms, provided to indicate robustness and not recommended for normal operation.

- [3] For duration < 10us, followed by sufficient time for the device to cool off.

- [4] As measured on DUT soldered on 2 oz Cu (FR4) PCB of size 1 square inch.

## 7.0 Recommended Operating Conditions

Table 4 Recommended Operating Conditions [1] @T<sub>J</sub> = +25 °C, unless otherwise specified.

| Parameter                             | Symbol          | Min | Nominal | Max  | Unit |

|---------------------------------------|-----------------|-----|---------|------|------|

| Input gate to Kelvin-source voltage   | V <sub>GS</sub> | 0   |         | 6.0  | V    |

| Pull-up resistor — with 12V drive [2] | D.:             | 25  |         |      | Ω    |

| Pull-up resistor — with 6V drive [2]  | R∪              | 10  |         |      | Ω    |

| Operating case temperature            | T <sub>C</sub>  | -40 |         | +125 | °C   |

### Note:

- [1] Operating for extended periods of time at conditions beyond the recommended range might affect device reliability.

- [2] The recommended value of this resistor depends on the drive type and the interface circuit. See the section on <u>Application Information</u> for more details.

## 8.0 Electrical Specifications

**Table 5 Electrical Specifications** <sup>[1]</sup> @T<sub>J</sub>= + 25°C, unless otherwise specified.

| Parameter              | Description                                   | Condition                                                                      | Minimum | Typical | Maximum | Unit |  |

|------------------------|-----------------------------------------------|--------------------------------------------------------------------------------|---------|---------|---------|------|--|

| Static Characteristics |                                               |                                                                                |         |         |         |      |  |

|                        | Drain to source                               | $I_{DS} = 0.5 \text{ A DC}, V_{GS} = 6 \text{ V},$<br>$T_{J} = +25 \text{ °C}$ |         | 180     | 236     |      |  |

| R <sub>DSON</sub>      | resistance                                    | I <sub>DS</sub> = 0.5 A DC, V <sub>GS</sub> = 6 V,<br>T <sub>J</sub> = +150 °C |         | 440     |         | mΩ   |  |

| Inco                   | Drain to source                               | V <sub>DS</sub> = 650 V, V <sub>GS</sub> = 0 V,<br>T <sub>J</sub> = +25 °C     |         | 0.2     |         | ^    |  |

| IDSS                   | leakage current                               | V <sub>DS</sub> = 650 V, V <sub>GS</sub> = 0 V,<br>T <sub>J</sub> = +150 °C    |         | 30.0    |         | μΑ   |  |

| V <sub>GS(th)</sub>    | Gate threshold voltage                        | $V_{DS} = V_{GS}$ ,<br>$I_{DS} = 5.5 \text{ mA}$                               |         | 1.7     | 2.5     | V    |  |

| I <sub>GS</sub>        | Gate to source current                        | V <sub>DS</sub> = 0 V,<br>V <sub>GS</sub> = 6 V                                |         | 13      |         | μΑ   |  |

|                        |                                               | Dynamic Characteristic                                                         | S       |         |         |      |  |

| Ciss                   | Input capacitance                             | - V <sub>DS</sub> = 400 V.                                                     |         | 55      |         | pF   |  |

| Crss                   | Reverse transfer capacitance                  | V <sub>S</sub> S = 400 V,<br>V <sub>S</sub> S = 0 V,<br>Freq = 100 kHz         |         | 0.32    |         | pF   |  |

| Coss                   | Output capacitance                            | F164 = 100 KHZ                                                                 |         | 18      |         | pF   |  |

| C <sub>O(ER)</sub> [2] | Effective output capacitance – energy related | V <sub>DS</sub> = 0 to 400 V,<br>V <sub>GS</sub> = 0 V                         |         | 26      |         | pF   |  |

| Co(TR) [3]             | Effective output capacitance – time related   | V <sub>DS</sub> = 0 to 400 V,<br>V <sub>GS</sub> = 0 V                         |         | 40      |         | pF   |  |

| Qoss                   | Output charge                                 | V <sub>DS</sub> = 400 V,<br>V <sub>GS</sub> = 0 V                              |         | 16      |         | nC   |  |

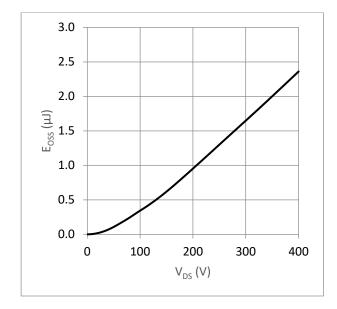

| Eoss                  | Output capacitance         | V <sub>DS</sub> = 400 V,<br>V <sub>GS</sub> = 0 V,                                           | 2.4           | μJ    |

|-----------------------|----------------------------|----------------------------------------------------------------------------------------------|---------------|-------|

| 2033                  | stored energy              | Freq = 100 kHz                                                                               |               | μο    |

|                       |                            | Gate Characteristics                                                                         |               |       |

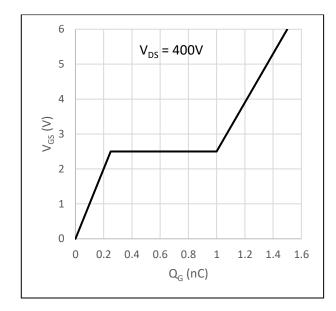

| Q <sub>G</sub>        | Gate charge – total        |                                                                                              | 1.5           | nC    |

| Q <sub>GS</sub>       | Gate to source charge      | V <sub>DS</sub> = 400 V<br>V <sub>GS</sub> = 0 to 6 V                                        | 0.25          | nC    |

| $Q_GD$                | Gate to drain charge       |                                                                                              | 0.75          | nC    |

| V <sub>GPLAT</sub>    | Gate plateau voltage       | V <sub>DS</sub> = 400 V<br>I <sub>DS</sub> = 4 A                                             | 2.5           | \ \ \ |

|                       | Re                         | everse Conduction Charact                                                                    | eristics      |       |

| Q <sub>RR</sub> [4]   | Reverse recovery charge    |                                                                                              | 0             | nC    |

| t <sub>RR</sub>       | Reverse recovery time      |                                                                                              | 0             | ns    |

| V <sub>SD</sub>       | Reverse conduction voltage | I <sub>SD</sub> = 2 A, V <sub>GS</sub> = 0 V<br>I <sub>SD</sub> = 6 A, V <sub>GS</sub> = 0 V | 2.5<br>4.0    | V     |

|                       | Switch                     | ing Time (Refer to Figure 4 a                                                                | and Figure 5) |       |

| t <sub>r</sub>        | Rise time                  |                                                                                              | 10            | ns    |

| t <sub>f</sub>        | Fall time                  | $V_{DS} = 400 \text{ V},$                                                                    | 5             | ns    |

| t <sub>prop-on</sub>  | Turn-on propagation delay  | $I_{DS} = 4 A,$ $R_{U} = 10 \Omega,$                                                         | 8             | ns    |

| t <sub>prop-off</sub> | Turn-off propagation delay | $R_D = 5 \Omega$                                                                             | 12            | ns    |

#### Note:

- [1] All V<sub>GS</sub> refer to the gate-to-source voltage of the respective power device. Note that the source and the Kelvin-source terminals are internally connected for each device.

- [2]  $C_{O(ER)}$  is an equivalent (fixed) capacitance that gives the same energy as  $C_{OSS}$  while  $V_{DS}$  rises from zero volt to the stated  $V_{DS}$ .

- [3]  $C_{O(TR)}$  is an equivalent (fixed) capacitance that gives the charging time as  $C_{OSS}$  while  $V_{DS}$  rises from zero volt to the stated  $V_{DS}$ .

- [4] Q<sub>RR</sub> computation excludes Q<sub>OSS</sub>.

### 9.0 About Gate Drive Requirements of GaN Power HEMT

### 9.1 Gate Drive Level, Slew-rate Control

The GaN HEMT has a recommended gate drive high voltage of +6 V, and hence the gate should operate between 0 to 6 V. A lower than optimum on-state gate drive high voltage, say 5.5 V or 5 V will result into a slightly higher R<sub>DSON</sub>. Before settling to a 6 V on-state voltage, if the gate voltage has some transient ringing (say, within 0.5 V), then the device can tolerate this without much adverse effect to the gate reliability. However, excessive ringing shall be avoided by minimizing the inductance of the gate drive loop. For a high-performance gate drive, the pull-up path and the pull-down path shall be kept separate,

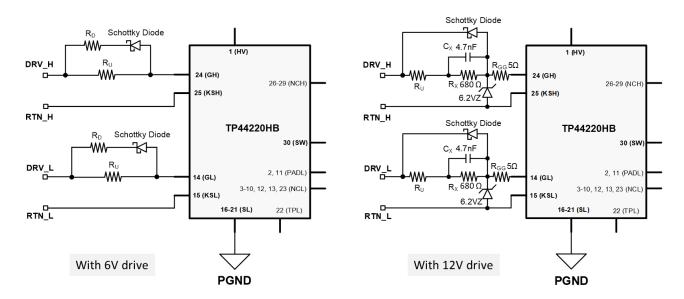

where the pull-up path resistor can be selected for controlling the turn-on slew-rate. This is similar to what is used for a common silicon power MOSFET. Recommended gate drive interface circuits both with 6 V and 12 V drivers are shown in the section <u>Application Information</u>.

## 9.2 Immunity Against Parasitic Turn-on, and Use of Negative Gate Drive

Switching produces dv/dt at the switch node, which in the case of GaN can be large. Apart from EMI issues, these large dv/dt may also lead to what is known as parasitic turn-on or Miller turn-on. The way this happens is that when one of the devices in H-bridge configuration turns-on under hard-switching, the drain-source voltage across the other device undergoes a rapid rise. This positive dv/dt on the drain of the other device (with respect to the gate/source) tries to turn it on through the parasitic gate-to-drain capacitance C<sub>GD</sub>. This parasitic turn-on is highly undesirable as it can cause catastrophic amount of shoot-through or crowbar current. An effective way to avoid such turn-on is to use low (or zero) pull-down resistance and to keep the inductance of the turn-off path low.

One way to avoid parasitic turn-on in GaN HEMT devices is to use a negative-swing gate-drive where under the off condition, the gate drive voltage is a negative voltage in the range of -2 V to -4 V. However, such a drive is more complex to implement and also causes higher losses under reverse conduction. The suggested way to avoid parasitic turn-on for Tagore's TP44220HB devices is to minimize the resistance and the loop inductance of the turn-off path. A good approach to minimize the turn-off resistance is to use a driver with a separate (and strong) turn-off path and use no external resistance in this path.

### 9.3 Thermal Pad Connection

In TP44220HB, there are two exposed thermal pads, both of which are available at the bottom side. The pad named TPL (Pin-22) is for the low-side device, and the pad named SW (Pin-30) is for the high-side device. For a desirable level of thermal performance, each of these pads need to be connected to a suitable heat-sink arrangement, or to (their own) large enough PCB islands. The connections can be either direct or through thermal vias with a pattern as shown in Figure 21. For the low-side device, it shall be noted that the thermal pad is connected to the device's substrate whereas the source connection of the device is brought out separately on Pins 16–21. This allows for insertion of current sense resistor at the low-side source without cutting the thermal path. However, care shall be exercised that the voltage difference between the TPL pad and Pins 16–21 shall not exceed ±20 V. For the high-side device, the pin SW is already connected both to the device's substrate and the source, and hence no special care is needed.

### 9.4 Kelvin Source for Gate Drive Loop

TP44220HB has separate Kelvin-source pins available for both the low-side and the high-side devices. These pins shall be used in the respective driver return paths for the best de-coupling of the gate-loops from the power-loops.

## 9.5 Parallel Operation for Higher Current

The device has a maximum current rating as given in Table 3. Higher current operation is possible if two or more TP44220HB devices are connected in parallel. For parallel operation, there are two main challenges. (1) One is the possibility of parasitic divergent oscillations between the parallel devices leading to permanent failure of devices. Such oscillations can happen in any type of two parallel power devices, but due to the extra-high speed of GaN devices, more care is needed. A major part of fixing such oscillations is to use individual gate resistors for each of the parallel devices (as opposed to using a single common resistor). Further, each individual Kelvin-source shall have a series resistor. (2) The other challenge of paralleling power devices is the imbalance of currents between the devices during the operation. Fortunately, GaN devices have a R<sub>DSON</sub> which has a positive temperature co-efficient. Therefore, between parallel devices, any imbalance in current is limited due to the negative feedback arising from this behavior. To aid dynamic balancing of current, it is highly recommended to make the layout as symmetric as possible. The individual series resistor of Kelvin-source further aids with this balancing. Finally, as with any arrangement of parallel devices, some derating shall be allowed.

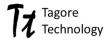

## **10.0 Switching Time Measurement Information**

The switching time parameters are measured using the test circuit shown in Figure 4. Here a TP44220HB device is configured in the well-known arrangement of double-pulse-test (DPT). The pin SW is connected to a 400 V DC bus supply through an inductor. The low-side power device is used as a controlled device, whereas the high-side power device is used in a freewheeling/clamp-diode mode (i.e., its gate GH is shorted to its Kelvin-source KSH). The two resistors R<sub>U</sub> and R<sub>D</sub> as shown in the figure are used for controlling the switching speed.

When the gate pin GL of the low-side of TP44220HB is supplied with a 6V signal, the low-side HEMT device turns on and the switch-node SW goes down to a low voltage as shown in Figure 5. During this time, the inductor current starts to increase. When the gate signal at GL is made low, the low-side HEMT device turns off, and hence, the switch-node SW starts to increase with a slew rate which depends on the inductor current and the switch-node capacitance. Once the switch-node reaches the DC bus and crosses it by about  $V_{GS(th)}$ , the high-side of TP44220HB turns on. Then, the switch-node voltage gets clamped to the DC bus voltage and remains so till the inductor current reaches zero.

The various switching including propagation delays are defined in Figure 5.

**Figure 4 Switching Time Measurement Circuit**

Figure 5 Switching Time Waveform and Definition of Parameters

## 11.0 Typical Characteristics

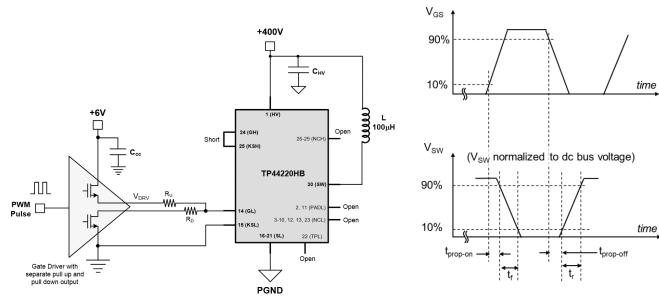

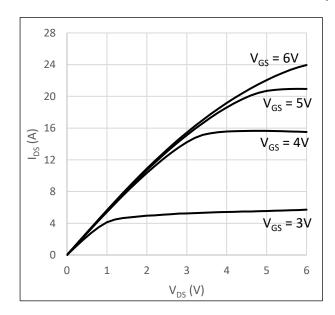

**Conditions:** @T<sub>J</sub> = +25 °C unless otherwise specified. Plots show behavior of a single device.

Figure 6 Forward Conduction of GaN HEMT  $I_{DS} = f(V_{DS}, V_{GS})$

Figure 7 Reverse Conduction of GaN HEMT  $I_{SD} = f(V_{SD}, V_{GS})$

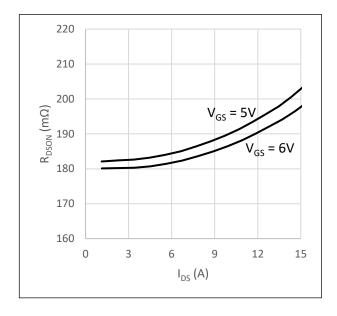

Figure 8 On-state Resistance of GaN HEMT  $R_{DSON} = f(I_{DS}, V_{GS})$

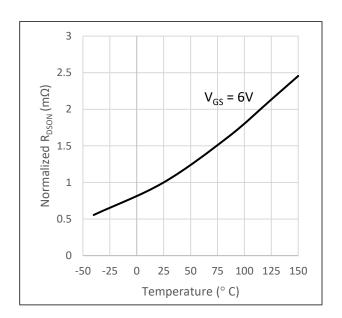

Figure 9 Normalized  $R_{DSON}$  vs. Junction Temperature at  $I_{DS} = 1$  A

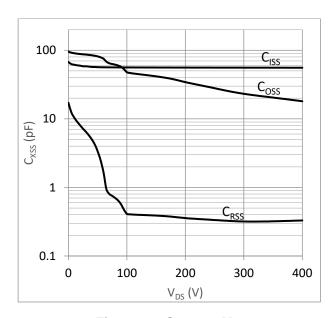

Figure 10 C<sub>XSS</sub> vs. V<sub>DS</sub>

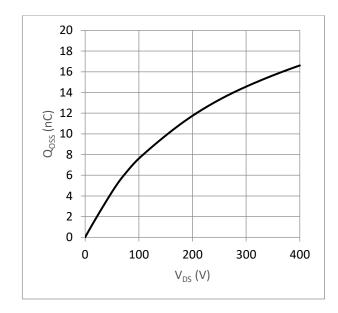

Figure 11 Qoss vs. VDS

Figure 12 Eoss vs. VDS

Figure 13 V<sub>GS</sub> vs. Q<sub>G</sub>

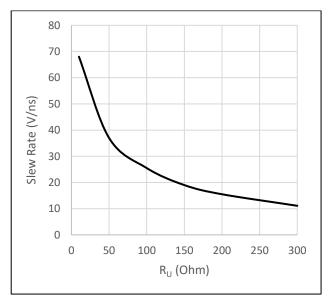

Figure 14 Drain Slew-Rate Variation vs. R<sub>U</sub> Resistor at Turn-On Transition [1]

### Note:

[1] The measurement setup is as per Figure 4 and Figure 5. The slew-rate corresponds to the region where SW drops from 90% to 10% of the bus voltage during its falling edge transition, and the value of  $I_{DS}$  at the transition is 4 A.

## 12.0 Application Information

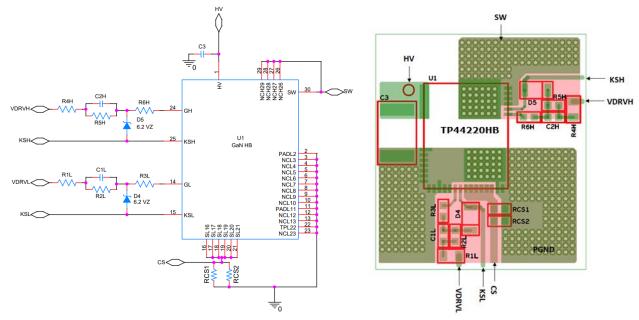

### 12.1 Interface for 6 V Drive

A TP44220HB device can be directly driven with a 6 V driver. However, typically, one needs to control turn-on/off speeds, for which resistors are used. For the common case of a driver with a single output (i.e., no dedicated pull-up and pull-down paths), the interface circuit is shown in the left-side diagram in Figure 15. The resistor  $R_U$  provides the path for turn-on, and its value can be selected for a desirable slew-rate. The turn-off path consists of  $R_U$  in parallel with a (Schottky +  $R_D$ ) combination. The job of the Schottky diode is to ensure that  $R_D$  only conducts during the turn off. Typically, a low value of  $R_D$  is preferred in order to avoid Miller turn-on as explained in Section 9.1. For the highest turn-off speed, the resistor  $R_D$  may be replaced by a short.

Some drivers have separate pull-up and pull-down paths. In such cases, no Schottky diode is needed, and the interface circuit simplifies to what was shown in Figure 4.

Figure 15 Gate Drive Interface (Left) for 6 V Drive, (Right) for ≥12 V Drive

### 12.2 Interface for ≥12 V Drive

When using a higher than 6 V drive (say a standard 12 V or higher), one can use an interface circuit shown in the right-side diagram in Figure 15. Zener diodes of 6.2 V serve the purpose of limiting the voltage between the gates and the Kelvin sources of both of the low-side or the high-side devices. The 5  $\Omega$  resistors  $R_{GG}$  connected to pins GL/GH are to avoid parasitic oscillation between the GaN device and the Zener diodes. For ZVS operation, these  $R_{GG}$  resistors are optional and may be removed by shorting. The resistors  $R_{U}$ , once again, are for setting the turn-on speed. In this diagram, for the maximum turn-off speed,  $R_{D}$  has been removed by shorting. The Schottky diodes remain to provide the fast turn-off path. Finally, within the resistor-capacitor pair  $R_{X}$ - $C_{X}$ , the resistor limits the Zener current during gate high periods. And the purpose of the capacitor  $C_{X}$  is to bypass  $R_{X}$  during transients so that the turn-on/off speed are not affected by  $R_{X}$ . This interface circuit can be used for other drive voltages which are higher than 6 V e.g., 9 V, 12V, 15 V etc. The value of  $R_{X}$  needs to be adjusted accordingly.

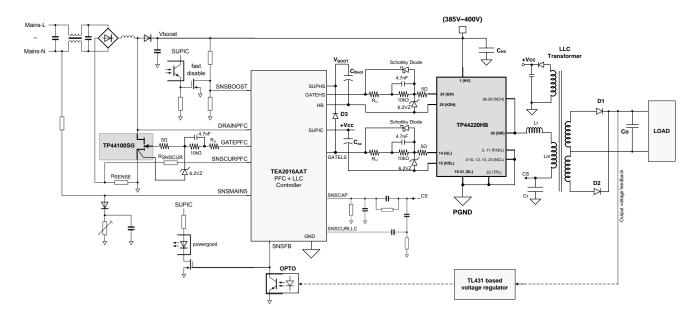

## 12.3 Example Application: AC-DC Power Conversion

This section presents the application of TP44220HB in ac-dc power conversion using a PFC followed by an LLC topology as shown in Figure 16. The combo-controller IC TEA2016AAT drives both the PFC and the LLC devices. The half-bridge LLC resonant converter needs two switching devices, for which this half-bridge GaN IC TP44220HB is used. Compared to a two discrete power devices solution, the single half-bridge IC significantly simplifies the PCB layout complexities, occupies less PCB foot-print area, reduces BOM part count and enables higher switching-frequency operation.

In the PFC section, Tagore's GaN HEMT part TP44100SG can be used as the main switching device. The combo controller IC TEA2016AAT outputs +12 V/0 V gate drive pulses for both the high- and low-side devices. The GaN half-bridge IC and the stand-alone GaN IC, however, need +6 V/0 V gate drive. To meet this requirement, the interface circuit of Section 12.2 has been used as shown in Figure 16. The turn-on speed of the GaN devices can be easily controlled through the resistor R<sub>U</sub>.

The secondary side of the LLC resonant converter is shown to have diode rectifiers D1 and D2. If desired, these diodes can be replaced with synchronous rectification FETs to achieve higher efficiency and better thermal performance.

Figure 16 AC-DC Power Converter Using a TP44220HB Part

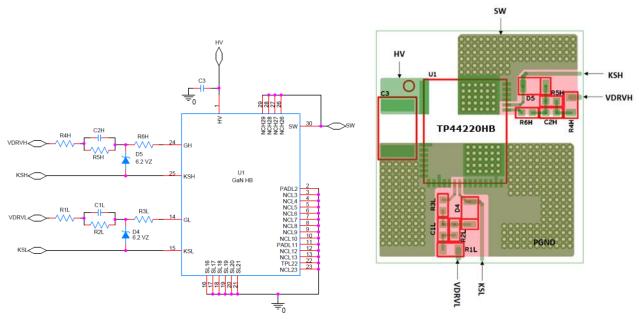

## 12.4 PCB Layout with and without Current-Sense Resistor

In a half-bridge, it is quite common to use a current sense resistor at the source side of the low-side device. Such as arrangement is shown in the top left drawing in Figure 17. While doing the layout for such cases, the thermal pad TPL (Pin-22) shall be connected to a large enough area on the PCB (the thermal plane) for heat dissipation. Usually, power-ground (PGND) is the largest copper area available, and the recommended layout is shown in the top right drawing in Figure 17 where PGND acts as the thermal plane. Note that with Tagore's TP44220HB parts, even with the sense resistors between the source pins and the thermal plane, the thermal performance of the low-side device is minimally affected. For the case when no sense resistors are used, one could short all the source pins with TPL (Pin-22) and use a layout as shown in the bottom right drawing in Figure 17.

(a) With current-sense resistors. IC sits on the green layer of PCB.

(b) Without current-sense resistors. IC sits on the green layer of PCB.

Figure 17 Layout Guidelines for (a) With the Current-Sense Resistors, and (b) Without the Current-Sense Resistors

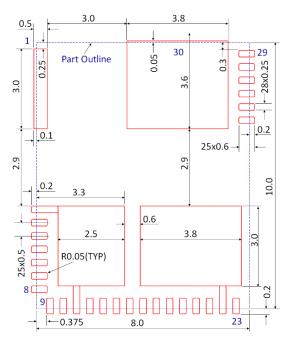

## 13.0 Device Package Information

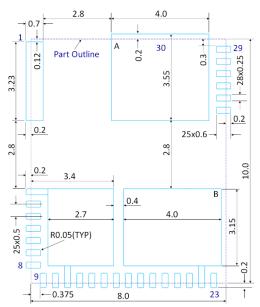

Figure 18 Device Package Drawing

(All dimensions are in mm)

**Table 6 Device Package Dimensions**

| Dimension | Value (mm) | Tolerance (mm) | Dimension | Value (mm) | Tolerance (mm) |

|-----------|------------|----------------|-----------|------------|----------------|

| Α         | 0.80       | ±0.05          | L         | 0.40       | ±0.05          |

| b         | 0.25       | +0.05/-0.07    | S1        | 0.70       | ±0.05          |

| D         | 8.00 BSC   | ±0.05          | S2        | 2.80       | ±0.05          |

| D1        | 4.00       | ±0.05          | S3        | 0.12       | ±0.05          |

| D2        | 0.38       | ±0.05          | S4        | 2.80       | ±0.05          |

| D3        | 3.98       | ±0.05          | S5        | 0.70       | ±0.05          |

| D4        | 2.70       | ±0.05          | S6        | 0.70       | ±0.05          |

| е         | 0.50 BSC   | ±0.05          | S7        | 0.75       | ±0.05          |

| Е         | 10.00 BSC  | ±0.05          | S8        | 0.30       | ±0.05          |

| E1        | 3.23       | ±0.05          | S9        | 0.30       | ±0.05          |

| E2        | 3.23       | ±0.05          | S10       | 0.375      | ±0.05          |

| E3        | 3.15       | ±0.05          | S11       | 0.40       | ±0.05          |

| E4        | 3.15       | ±0.05          | -         | -          | -              |

**Note:** Lead finish: Pure Sn without underlayer; Thickness: 7.5 μm ~ 20 μm (Typical 10 μm ~ 12 μm)

### Attention:

Please refer to application notes  $\underline{TN-001}$  and  $\underline{TN-002}$  at http://www.tagoretech.com for PCB and soldering related guidelines.

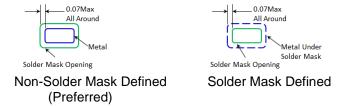

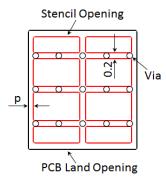

## 14.0 PCB Land Design

#### **Guidelines:**

- [1] A 4-layer PCB is recommended.

- [2] Via diameter is recommended to be 0.3mm to prevent solder wicking inside the vias.

- [3] Thermal vias shall only be placed on pad A, B, and C.

- [4] The maximum via number for pads A, B, and C are  $6(X)\times5(Y)=30$ ,  $6(X)\times5(Y)=30$  and  $4(X)\times5(Y)=20$ , respectively.

Figure 19 PCB Land Pattern

(Dimensions are in mm)

Figure 20 Solder Mask Pattern

(Dimensions are in mm)

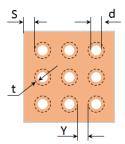

Figure 21 Thermal Via Pattern

(Recommended Values:  $S \ge 0.15$  mm;  $Y \ge 0.20$  mm; d = 0.3 mm; Plating Thickness t = 25  $\mu$ m or 50  $\mu$ m)

## 15.0 PCB Stencil Design

### **Guidelines:**

- [1] Laser-cut, stainless steel stencil is recommended with electro-polished trapezoidal walls to improve the paste release.

- [2] Stencil thickness is recommended to be 125 µm.

Figure 22 Stencil Openings (Dimensions are in mm)

Figure 23 Stencil Openings (Shall Not Cover Via Areas if Possible)

(Dimensions are in mm)

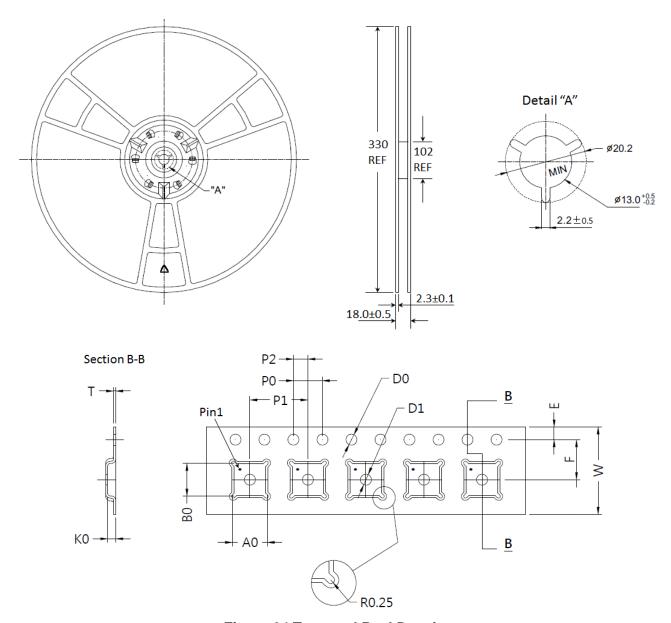

# 16.0 Tape and Reel Information

Figure 24 Tape and Reel Drawing

**Table 7 Tape and Reel Dimensions**

| Dimension | Value (mm) | Tolerance (mm) | Dimension | Value (mm) | Tolerance (mm) |

|-----------|------------|----------------|-----------|------------|----------------|

| A0        | 10.35      | ±0.10          | K0        | 1.10       | ±0.10          |

| B0        | 8.35       | ±0.10          | P0        | 4.00       | ±0.10          |

| D0        | 1.50       | +0.10/-0.00    | P1        | 8.00       | ±0.10          |

| D1        | 1.50       | +0.10/-0.00    | P2        | 2.00       | ±0.05          |

| Е         | 1.75       | ±0.10          | Т         | 0.30       | ±0.05          |

| F         | 5.50       | ±0.05          | W         | 12.00      | ±0.30          |

Revision 1.3 - 2023-09-08

**Edition** Revision 1.3 - 2023-09-08

### **Published by**

Tagore Technology Inc. 601 W Campus Drive Suite C1, Arlington Heights, IL 60004, USA

©2023-24 All Rights Reserved

### **Legal Disclaimer**

The information provided in this document shall in no event be regarded as a guarantee of conditions or characteristics. Tagore Technology assumes no responsibility for the consequences of the use of this information, nor for any infringement of patents or of other rights of third parties which may result from the use of this information. No license is granted by implication or otherwise under any patent or patent rights of Tagore Technology. The specifications mentioned in this document are subject to change without notice.

#### For Further Information

For further information on technology, delivery terms and conditions and prices, please contact Tagore Technology: support@tagoretech.com.